# Skript Analogelektronik Kap 0 Einführung: (noch unvollständig)

- 0. Einführung ... (wird noch ausgeführt) ... 0.1. Vorbemerkungen ... (wird noch ausgeführt) ... 0.2. Kenntnissen und Methoden ... (wird noch ausgeführt) ... a) Mathematische Gesetze und Methoden (siehe Skript "web 2010 Elektronik Script Grundlagen.pdf" Physikalische Gesetze und Methoden b) (siehe Skript "web 2010 Elektronik Script Grundlagen.pdf" Grundlagen der Elektrotechnik c) (siehe Skript "web\_2010\_Elektronik\_Script\_Grundlagen.pdf" - Ladungsträgertrennung, Potenzial, Spannung, Strom - Gesetzmäßigkeiten im Grundstromkreis (Quelle, Innen- und Lastwiderstand, Belastungsfälle, ZP-Theorie ...) - Ersatzschaltungen für Spannungs- und Stromquellen d) Das elektronische Bauelement in der Schaltung d.1 Strom – Spannungs – Kennlinie (I – U –KL) d.2 Ersatzschaltbild d.3 Berechnungsverfahren d.4 Arbeitspunkt, Bauelemente – Temperatur, Wärmeableitung 0.3. Halbleitertechnik ... (wird noch ausgeführt) ... 0.3.1. Einteilung der Festkörper ... (wird noch ausgeführt) ...

- 0.3.2. Eigenleitfähigkeit (i-Leitung)

- ... (wird noch ausgeführt) ...

- 0.3.3. Störstellenleitfähigkeit / Dotierung (p- und n-Leitung)

- ... (wird noch ausgeführt) ...

0.3.3.1. p – Halbleiter

... (wird noch ausgeführt) ...

0.3.3.2. n – Halbleiter

... (wird noch ausgeführt) ...

0.3.4. pn - Übergang

... (wird noch ausgeführt) ...

0.3.4.1. pn – Übergang ohne äußere Spannung

... (wird noch ausgeführt) ...

0.3.4.2. pn – Übergang mit äußerer Spannung

... (wird noch ausgeführt) ...

a) Durchlassrichtung

... (wird noch ausgeführt) ...

b) Sperrrichtung

... (wird noch ausgeführt) ...

0.3.5. Metall - HL - Übergang

... (wird noch ausgeführt) ...

0.4. Integrierte Schaltungen

... (wird noch ausgeführt) ...

0.4.1. Chip – Herstellung (Übersicht)

### 0.4.2. Basistechnologien

#### a) Bipolar - Technik

Die Bipolar-Technik ermöglicht die Erzeugung von Transistor-, Dioden-, Widerstands- und Kapazitätsfunktionen nebeneinander auf einem Chip.

Die zu integrierenden Bauelemente müssen voneinander isoliert werden.

#### Der Standard dafür besteht aus

- in Sperrrichtung vorgespannte pn-Übergänge.

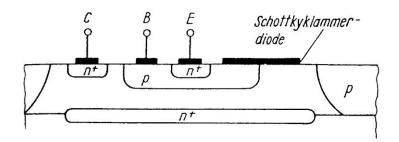

Bild 10 Bipolartransistor in SBC-Technik mit Schottkyklammerdiode

Weitere Technologien für die Isolierung sind:

- SiO2 - Trennwände beim Isoplanar-Verfahren und

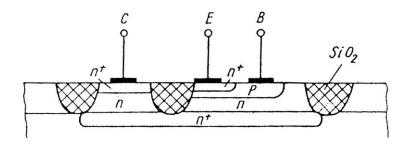

Bild 11 Bipolartransistor in Isoplanar-Technik

- dielektrische Isolation mittels Luft beim Beamlead-Verfahren.

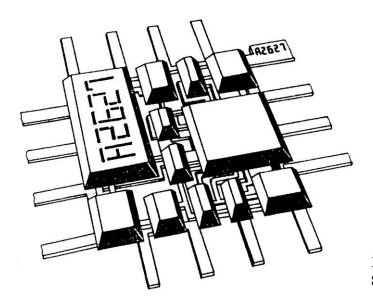

Bild 12 Schaltkreis in Beam-lead-Tech

### b) MIS - Technik (MOS)

bei dieser Technologie sind keine isolierten Inseln wie bei der Bipolar-Technik nötig, weil die MIS-Transistoren selbstisolierend sind.

Dafür müssen aber parisitäre Kanäle (besonders bei der n-Kanal-Technik) vermieden werden.

### Metallgatetechnik:

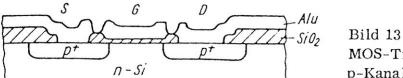

Es handelt sich hierbei um die älteste MIS-Basistechnologe in p-Kanal-Metallgatetechnik.

Die wichtigsten Eigenschaften sind:

- große parasitärer Kapazitäten (besonders am Gate) und

- die Ladungsträger (Löcher) haben eine geringe Beweglichkeit.

Beides führt zu bescheidenen elektrischen Kennwerten. Besonders die Geschwindigkeit (Taktfrequenz) fiel bescheiden aus (unter 1 MHz).

Bild 13 MOS-Transistor in p-Kanal-Metallgatetechnik

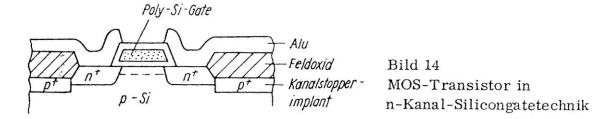

# Siliziumgatetechnik

Sie bildet die Basis für die moderne n-Kanal-Technik.

Die wichtigsten Eigenschaften sind:

- Verkleinerung der parasitären Gate-Kapazitäten und

- die Ladungsträger bestehen aus den schnellen Elektronen.

Das führt zu den verbesserten elektrischen Kennwerten. Bereits im ersten Anlauf konnten die Taktfrequenzen gegenüber der Metallgatetechnik um das 5- bis 10-fache vergrößert werden.

Verwendet wird die Siliziumgatetechnik für die Herstellung von Standardschaltkreisen für die Mikrorechentechnik (Prozessoren, Speicher ...) und für die Herstellung von kundenspezifischen Schaltkreisen.

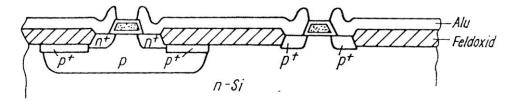

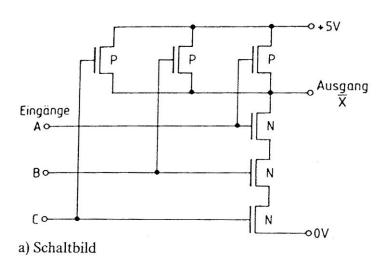

#### CMOS - Technik

CMOS bedeutet die gleichzeitige Verwendung von komplementären MOS-Transistoren. Bei der CMOS – Technik werden also p- und n-Kanal MOS-Transistoren gleichzeitig auf einem Chip realisiert.

Die so gebildeten Halbleiter-Schalter schalten niederohmig das Masse- oder das Betriebsspannungspotenzial an den Ausgang, nach dem die jeweilige Verarbeitungsfunktion (NOT, AND, OR ...) durchgeführt wurde.

Verwendet wird die CMOS-Technik für die Herstellung von Logikbausteinen der Reihen 4000 und 74HCTxxsowie für die Herstellung von CMOS-Speichern.

Bild 16. MOS-Transistoren in Silicongate-CMOS-Technik

### c) Integrierte Widerstände

Widerstände lassen sich auf der Oberfläche des HL-Materials (Chips) in Dünnfiltechnik aufbringen. Dabei wird die Widerstandsbahn aufgedampft.

Tafel 2. Parameter von Dünnschichtwiderständen

| Material      | Schichtwiderstand $R_S/\Omega$  | $TK/10^{-6} K^{-1}$ |  |

|---------------|---------------------------------|---------------------|--|

| NiCr          | 30 300                          | 100                 |  |

| Ta            | 10 100                          | 100                 |  |

| Ni<br>Poly Si | $10 \dots 10^5$ $50 \dots 10^7$ | 100                 |  |

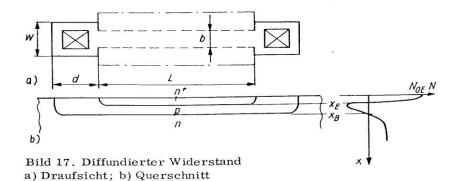

Der Querschnitt diffundierter Widerstände wird im Bild 17 gezeigt. Die Widerstandsschicht ist die diffundierte p-Schicht. Wie im Bild 17 gezeigt wird, kann der Querschnitt dieser p-Widerstandsschicht noch um die Tiefe xe einer n-Schicht eingeengt werden.

Nachteilig ist in beiden Fällen der recht hohe Flächenbedarf auf dem Chip.

# d) Integrierte Kapazitäten

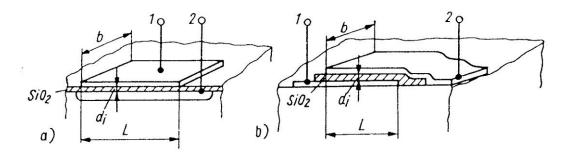

Kapazitäten lassen sich auf dreierlei Arten auf dem Chip integrieren. Dabei sind nur relativ kleine Kapazitätswerte (pF bis wenige nF) realisierbar.

# 1. Isolierschichtkapazitäten (2Varianten):

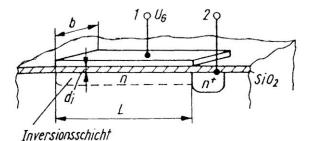

$$C_{12} = \frac{\varepsilon_i}{d_i} bL$$

.

Bild 18. Isolierschichtkapazitäten

- a) zwischen Deckelektroden und diffundierter niederohmiger Schicht,

- b) zwischen zwei Dünnschichtelektroden

#### 2. MOS-Kapazität:

Bild 19 MOS-Kapazität

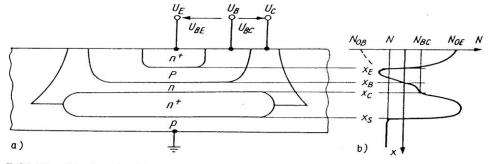

### 3. Sperrschichtkapazitäten bei der Bipolar-Technik:

Bild 20. Bipolarstruktur a) Querschnitt; b) Störstellenprofil

### e) Strukturbeispiel

Hier wird beispielhaft die Struktur eines CMOS-NAND-Bausteins gezeigt. Der NAND-Baustein mit 2 Eingängen besteht aus je 3 p-Kanal und n-Kanal MOS-Transistoren und deren Verschaltung. Aus dem unteren Bild lassen sich die Folien der einzelnen Ebenen während der Herstellung erahnen.

Bild 1.16 3-NAND-Gatter als Beispiel für eine Standardzelle

# 0.4.3. Integrationsgrade

Der Integrationsgrad ist ein Maß für die auf einem Chip untergebrachten funktionsbestimmenden Elemente (z.B. Anzahl der Transistorfunktionen, Anzahl der Speicherzellen ...).

Die Entwicklung verdeutlicht die folgende Tabelle:

| Bezeichn. d. Integrationsdichte | Abkürzung | Transitoren/Baustein            | ca. Jahr |

|---------------------------------|-----------|---------------------------------|----------|

| Diskreter Transistor            |           |                                 | 1951     |

| Small Scale Integration         | SSI       | < 10 <sup>2</sup>               | 1960     |

| Medium Scale Integration        | MSI       | 10 <sup>2</sup> 10 <sup>3</sup> | 1966     |

| Large Scale Integration         | LSI       | 10 <sup>3</sup> 10 <sup>4</sup> | 1969     |

| Very Large Scale Integration    | VLSI      | 10 <sup>4</sup> 10 <sup>5</sup> | 1975     |

| Ultra Large Scale Integration   | ULSI      | 10 <sup>5</sup> 10 <sup>6</sup> | 1989     |

| Super Large Scale Integration   | SLSI      | 10 <sup>6</sup> 10 <sup>7</sup> | 1992     |

| Extra Large Scale Integration   | ELSI      | 10 <sup>7</sup> 10 <sup>8</sup> | 1998     |

| Giga Scale Integration          | GSI       | 10 <sup>9</sup>                 | 2005     |

Einen Eindruck oder eine Vorstellung von der Entwicklung in der Mikroelektronik bekommt man auch, wenn man sich vergegenwärtigt, wie sich die Strukturbreiten bei der Chipfertigung in den letzten 20 Jahren entwickelt haben. 1989 wurden die Strukturen noch mit einem minimalen Abstand von ca. 700 nm gefertigt. Heute werden moderne Schaltkreise mit einem minimalen Abstand von 35 nm und jüngst mit 20 nm gefertigt.